Chris Jesshope Colin Egan (Eds.)

# Advances in Computer Systems Architecture

11th Asia-Pacific Conference, ACSAC 2006 Shanghai, China, September 2006 Proceedings

## Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Chris Jesshope Colin Egan (Eds.)

## Advances in Computer Systems Architecture

11th Asia-Pacific Conference, ACSAC 2006 Shanghai, China, September 6-8, 2006 Proceedings

Volume Editors

Chris Jesshope University of Amsterdam, Informatics Institute, School of Computer Science Kruislaan 403, 1098 SJ Amsterdam, The Netherlands E-mail: jesshope@science.uva.nl

Colin Egan University of Hertfordshire, School of Computer Science College Lane, Hatfield, Hertfordshire AL10 9AB, UK E-mail: c.egan@herts.ac.uk

Library of Congress Control Number: 2006931938

CR Subject Classification (1998): B.2, B.4, B.5, C.2, C.1, D.4

LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-40056-7 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-40056-1 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, IndiaPrinted on acid-free paperSPIN: 1185980206/31425 4 3 2 1 0

### Preface

On behalf of all of the people involved in the program selection, the program committee members as well as numerous other reviewers, we are both relieved and pleased to present you with the proceedings of the 2006 Asia-Pacific Computer Systems Architecture Conference (ACSAC 2006), which is being hosted in Shanghai on September 6–8, 2006.

This is the 11th in a series of conferences, which started life in Australia, as the computer architecture component of the Australian Computer Science Week. In 1999 it ventured away from its roots for the first time, and the fourth Australasian Computer Architecture Conference was held in the beautiful city of Sails (Auckland, New Zealand). Perhaps it was because of a lack of any other computer architecture conference in Asia or just the attraction of traveling to the Southern Hemisphere but the conference became increasingly international during the subsequent three years and also changed its name to include Computer Systems Architecture, reflecting more the scope of the conference, which embraces both architectural and systems issues. In 2003, the conference again ventured offshore to reflect its constituency and since then has been held in Japan in the beautiful city of Aizu-Wakamatsu, followed by Beijing and Singapore. This year it again returns to China and next year will move to Korea for the first time, where it will be organized by the Korea University.

To understand the scope and constituency of the conference, papers have been submitted from China, Taiwan, Korea, Japan, Australia, the UK, the Netherlands, Brazil, the USA, Norway, Sweden, Iran, Cyprus, India and Romania with the majority of papers coming from the Asia-Pacific region. The scope of the conference can be gleaned by looking at the diversity of submissions, which include papers on processor and network design, reconfigurable computing and operating systems, including both low-level design issues in hardware and systems as well as papers describing large and significant computer-based infrastructure projects. In keeping with the trends in this field, many of the papers that reflect the changing nature of computing systems and the constraints that the industry is working under. For example, there are many papers that reflect the move to concurrency on chip in multi-core devices, and many more are concerned with the significant problems industry will face with stricter budgets in power dissipation.

In addition to the submitted papers we have three keynote presentations. These presentations reflect the changing aspects of our industry as described above. Guang R. Gao, who is the Distinguished Professor of Electrical and Computer Engineering at Delaware University, will give a presentation on his work in programming chip multiprocessors and other highly concurrent systems. Gao's research is closely linked to IBM's recently announced cell processor, and he is developing compilers that enable thousands of processors to work together smoothly and efficiently by dividing various tasks among them. This work is conducted through the Computer Architecture and Parallel Systems Laboratory (CAPSL). Our second keynote speaker is from Europe and represents a key company in the embedded computer systems area. Vladimir Vasekin is a Russian Computer Scientist who was

recruited by ARM Ltd. in 2003. He started his career working in the Kronos Research Group at Novosibirsk University, developing the first 32-bit Russian workstations. While at ARM he has been involved in extensions to the ARM V6 architecture as well as in optimizing power dissipation in systems on chip. Our final invited speaker is Alex Shafarenko, who is professor of Software Engineering at the University of Hertfordshire in the UK and coordinator of the Compiler Technology and Computer Architecture Research Group (CTCA). Shafarenko is undertaking pioneering work in strongly-typed languages for coordinating concurrency in an asynchronous distributed environment.

Finally we would like to thank all of those who worked hard to make ACSAC 2006 a success this year. This includes all of the authors for submitting their work and the program committee and reviewers, without whose significant effort in producing reviews by our deadlines, we would have been unable to put this conference program together. Finally we thank the other General Chairs, Minglu Li of Shanghai Jiao Tong University and Minyi Guo from the University of Aizu for their effort in managing the conference arrangements and last and by no means least, Feilong Tang, also from Shanghai Jiao Tong University, who was in charge of local arrangements.

June 2006

Chris Jesshope Colin Egan

## Organization

## **General Chairs**

| University of Amsterdam, Netherlands |

|--------------------------------------|

| Shanghai Jia Tong University, China  |

| University of Aizu, Japan            |

|                                      |

## **Program Chair**

| Colin Egan | University of Hertfordshire, UK |

|------------|---------------------------------|

| •          |                                 |

## Local Arrangements Chair

Feilong Tang

Shanghai Jia Tong University, China

## **Program Committee**

| Vijayan Asari       | Old Dominion University, Norfolk, VA, USA      |

|---------------------|------------------------------------------------|

| Lim Hock Beng       | National University of Singapore               |

| Sangyeun Cho        | University of Pittsburgh, USA                  |

| Lynn Choi           | Korea University Seoul, South Korea            |

| Bruce Christianson  | University of Hertfordshire, UK                |

| Oliver Diessel      | University of New South Wales, Australia       |

| Colin Egan          | University of Hertfordshire, UK                |

| Skevos Evripidou    | University of Cyprus, Cyprus                   |

| Michael Freeman     | University of York, UK                         |

| Guang G. Gao        | CAPSL, University of Delaware, USA             |

| Jean-Luc Gaudiot    | University of California, Irvine, USA          |

| Alex Gontmakher     | Technion, Israel                               |

| Minyi Guo           | Aizu University, Japan                         |

| Gernot Heiser       | National ICT, Australia                        |

| Wei-Chung Hsu       | University of Minnesota, Twin-Cities, USA      |

| Chris Jesshope      | University of Amsterdam, Netherlands           |

| Hong Jiang          | University of Nebraska-Lincoln, USA            |

| Jeremy Jones        | Trinity College, Dublin, Ireland               |

| Norman P. Jouppi    | Hewlett Packard, USA                           |

| Feipei Lai          | National Technological University, Walden, USA |

| Minglu Li           | Shanghai Jiao Tong University, China           |

| Philip Machanick    | University of Queensland, Australia            |

| Worawan Marurngsith | Thammasat University, Bangkok, Thailand        |

| Henk Muller         | University of Bristol, UK                      |

| Sukumar Nandi       | Indian Institute of Technology Guwahati, India |

| Tin-Fook Ngai       | Intel China Research Center, China             |

|                     |                                                |

Amos Omondi L M Patnaik Andy Pimentel **Ronald Pose** Stanislay G. Sedukhin Won Shim Mark Smotherman K. Sridharan Paul Stravers Feilong Tang Rajeev Thakur Mateo Valero Stamatis Vassiliadis Lucian N. Vintan Tanya Vladimirova Wong Weng Fai Chengyong Wu Jingling Xue Pen-Chung Yew

#### **Co-reviewers**

Ahmed Zekri Andrei Terechko Antonia Zhai Arun Arvind Cees de Laat Costas Kyriacou **Daniel Rolls Dmitry Cheresiz** Herman ter Horst Huiyang Zhou Hyunjin Lee James A. Malcolm Jason Holdsworth Jason McGuiness Jinpyo Kim Joe Ryan Kanad Chakraborty Kim Marshall Kyueun Yi Lei Jin Lian Li Long Chen Lotfi Mhamdi

Yonsei University, Seoul, South Korea Indian Institute of Science, Bangalore, India University of Amsterdam, Netherlands Monash University, Australia The University of Aizu, Japan SNUT. South Korea Clemson University, USA Indian Institute of Technology Madras, India Philips Research, Netherlands Shanghai Jiao Tong University, China Argonne National Laboratory, USA Technical University of Catalonia, Spain University of Delft, Netherlands "Lucian Blaga" University of Sibiu, Romania University of Surrey, UK National University of Singapore, Singapore Chinese Academy of Sciences, China University of New England, Armidale, Australia University of Minnesota, Twin-Cities, USA

> Manvi Agarwal Marc Daumas Marios Mavronicolas Michael Hicks Murali Vilayannur Patrick (Boggle) Ouick Pavlos Moraitis Pedro Trancoso Peter Tische Raikumar Kettimuthu Ramón Beivide Renato Hentschke Rob Latham Sam Lang Sanghoon Lee Shaoshan Liu Thomas Bernard Toshiaki Miyazaki Venkatesan Packirisamy Won Woo Ro Yuichi Okuyama Zhi-Li Zhang

## Table of Contents

| The Era of Multi-core Chips -A Fresh Look on Software Challenges $\ldots \ldots$ Guang R. Gao                                            | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Streaming Networks for Coordinating Data-Parallel Programs (Position<br>Statement)                                                       | 2   |

| Implementations of Square-Root and Exponential Functions for Large<br>FPGAs                                                              | 6   |

| Using Branch Prediction Information for Near-Optimal I-Cache<br>Leakage<br>Sung Woo Chung, Kevin Skadron                                 | 24  |

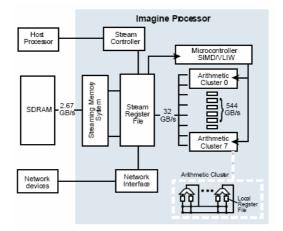

| Scientific Computing Applications on the Imagine Stream Processor<br>Jing Du, Xuejun Yang, Guibin Wang, Fujiang Ao                       | 38  |

| Enhancing Last-Level Cache Performance by Block Bypassing and<br>Early Miss Determination                                                | 52  |

| A Study of the Performance Potential for Dynamic Instruction Hints<br>Selection                                                          | 67  |

| Reorganizing UNIX for Reliability<br>Jorrit N. Herder, Herbert Bos, Ben Gras, Philip Homburg,<br>Andrew S. Tanenbaum                     | 81  |

| Critical-Task Anticipation Scheduling Algorithm for Heterogeneous<br>and Grid Computing<br>Ching-Hsien Hsu, Ming-Yuan Own, Kuan-Ching Li | 95  |

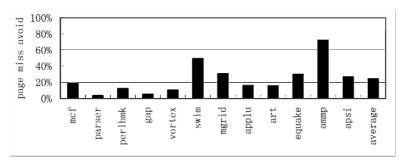

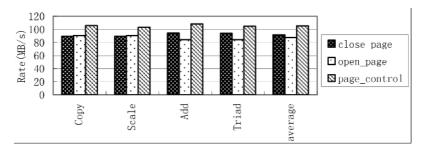

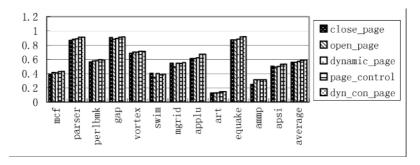

| Processor Directed Dynamic Page Policy<br>Dandan Huan, Zusong Li, Weiwu Hu, Zhiyong Liu                                                  | 109 |

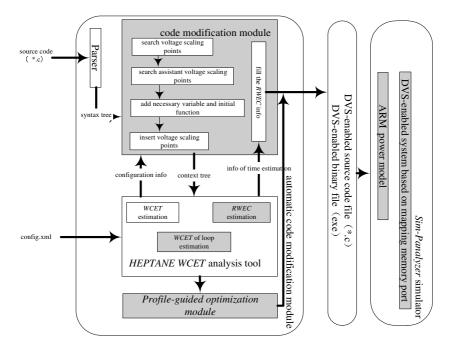

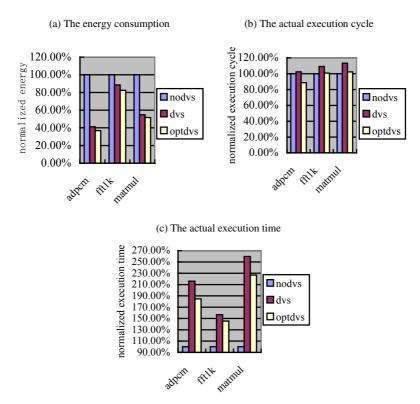

| Static WCET Analysis Based Compiler-Directed DVS Energy<br>Optimization in Real-Time Applications                                        | 123 |

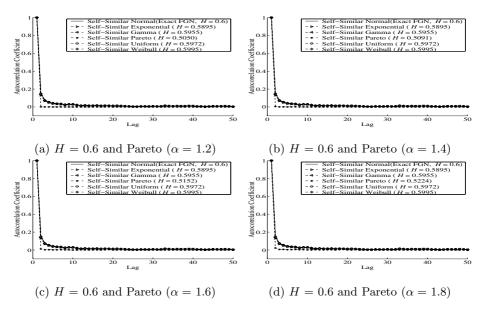

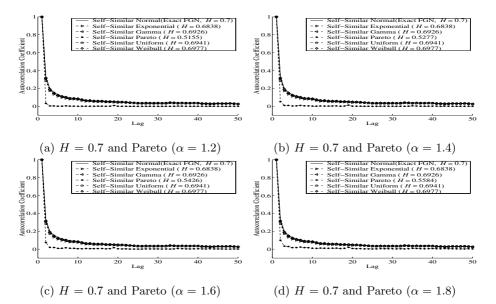

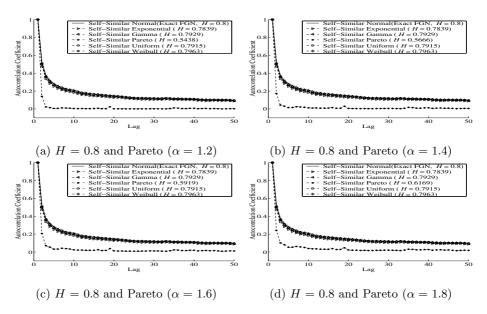

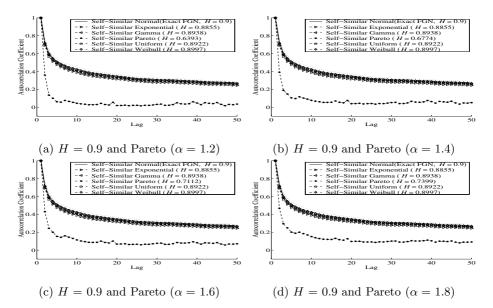

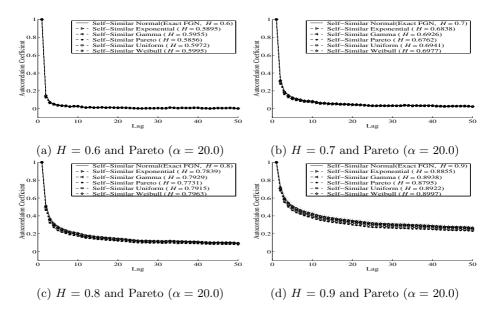

| A Study on Transformation of Self-similar Processes with Arbitrary<br>Marginal Distributions<br>Hae-Duck J. Jeong, Jong-Suk R. Lee                                                                                                          | 137 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $\mu {\rm TC}$ – An Intermediate Language for Programming Chip<br>Multiprocessors                                                                                                                                                           | 147 |

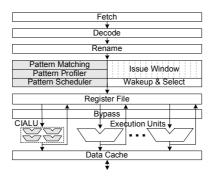

| Functional Unit Chaining: A Runtime Adaptive Architecture for<br>Reducing Bypass Delays<br>Lih Wen Koh, Oliver Diessel                                                                                                                      | 161 |

| Trace-Based Data Cache Leakage Reduction at Link Time<br>Lian Li, Jingling Xue                                                                                                                                                              | 175 |

| Parallelizing User-Defined and Implicit Reductions Globally on<br>Multiprocessors                                                                                                                                                           | 189 |

| Overload Protection for Commodity Network Appliances<br>Luke Macpherson                                                                                                                                                                     | 203 |

| An Integrated Temporal Partitioning and Mapping Framework<br>for Handling Custom Instructions on a Reconfigurable Functional<br>Unit<br>Farhad Mehdipour, Hamid Noori, Morteza Saheb Zamani,<br>Kazuaki Murakami, Mehdi Sedighi, Koji Inoue | 219 |

| A High Performance Simulator System for a Multiprocessor System<br>Based on a Multi-way Cluster<br>Arata Shinozaki, Masatoshi Shima, Minyi Guo, Mitsunori Kubo                                                                              | 231 |

| Hardware Budget and Runtime System for Data-Driven Multithreaded<br>Chip Multiprocessor                                                                                                                                                     | 244 |

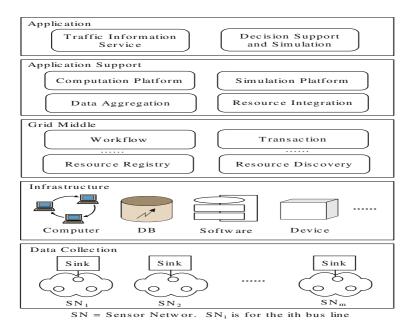

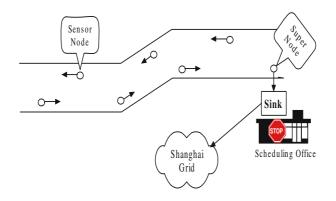

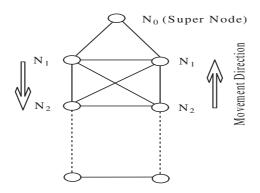

| Combining Wireless Sensor Network with Grid for Intelligent City<br>Traffic                                                                                                                                                                 | 260 |

| A Novel Processor Architecture for Real-Time Control<br>Xiaofeng Wu, Vassilios Chouliaras, Jose Nunez-Yanez,<br>Roger Goodall, Tanya Vladimirova                                                                                            | 270 |

| A 0-1 Integer Linear Programming Based Approach for Global Locality<br>Optimizations<br>Jun Xia, Li Luo, Xuejun Yang                                                                                           | 281 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

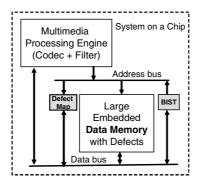

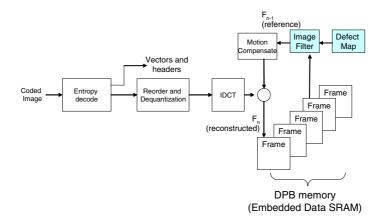

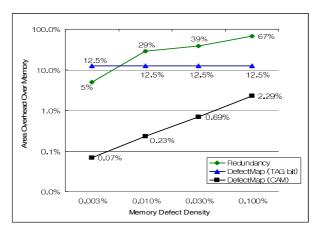

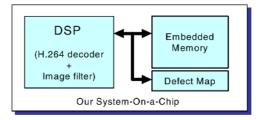

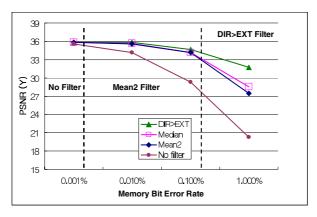

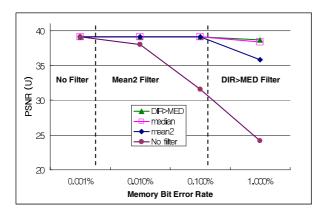

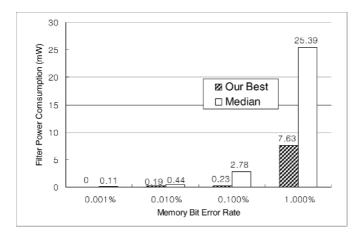

| Design and Analysis of Low Power Image Filters Toward<br>Defect-Resilient Embedded Memories for Multimedia SoCs<br>Kang Yi, Kyeong Hoon Jung, Shih-Yang Cheng, Young-Hwan Park,<br>Fadi Kurdahi, Ahmed Eltawil | 295 |

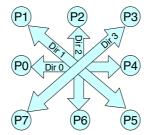

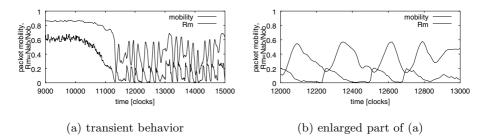

| Entropy Throttling: A Physical Approach for Maximizing Packet<br>Mobility in Interconnection Networks<br>Takashi Yokota, Kanemitsu Ootsu, Fumihito Furukawa,<br>Takanobu Baba                                  | 309 |

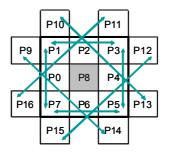

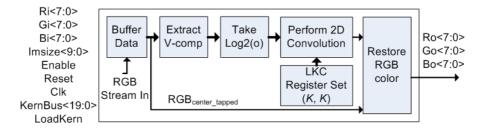

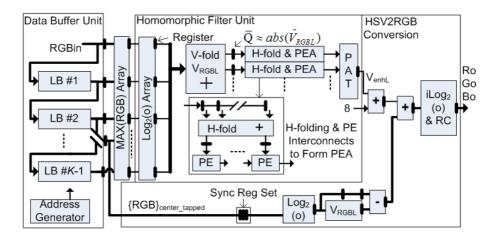

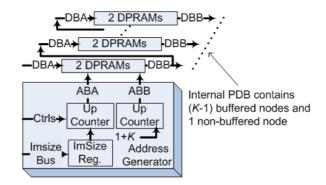

| Design of an Efficient Flexible Architecture for Color Image<br>Enhancement<br>Ming Z. Zhang, Li Tao, Ming-Jung Seow, Vijayan K. Asari                                                                         | 323 |

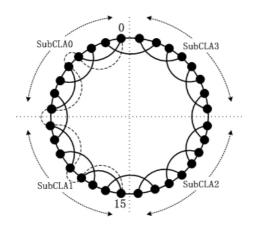

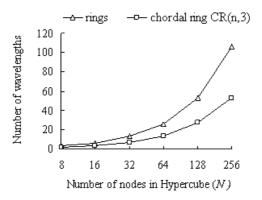

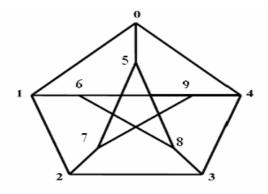

| Hypercube Communications on Optical Chordal Ring Networks<br>with Chord Length of Three<br>Yawen Chen, Hong Shen, Haibo Zhang                                                                                  | 337 |

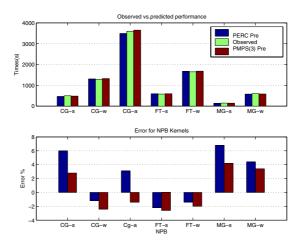

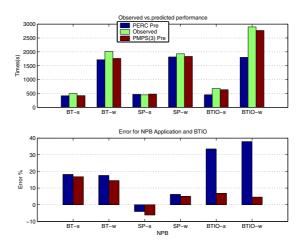

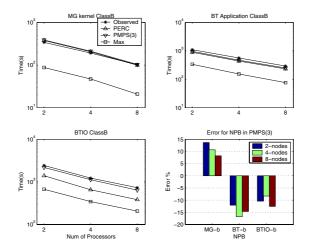

| PMPS(3): A Performance Model of Parallel Systems<br>Yong-ran Chen, Xing-yun Qi, Yue Qian, Wen-hua Dou                                                                                                          | 344 |

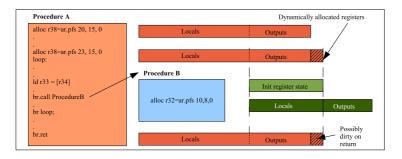

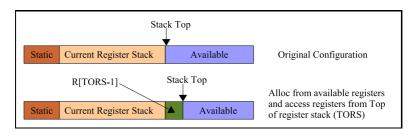

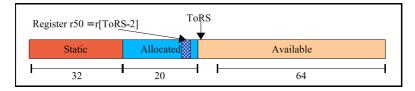

| Issues and Support for Dynamic Register Allocation<br>Abhinav Das, Rao Fu, Antonia Zhai, Wei-Chung Hsu                                                                                                         | 351 |

| A Heterogeneous Multi-core Processor Architecture for High<br>Performance Computing<br>Jianjun Guo, Kui Dai, Zhiying Wang                                                                                      | 359 |

| Reducing the Branch Power Cost in Embedded Processors Through<br>Static Scheduling, Profiling and SuperBlock Formation<br>Michael Hicks, Colin Egan, Bruce Christianson, Patrick Quick                         | 366 |

| Fault-Free Pairwise Independent Hamiltonian Paths on Faulty<br>Hypercubes                                                                                                                                      | 373 |

| Constructing Node-Disjoint Paths in Enhanced Pyramid Networks<br>Hsien-Jone Hsieh, Dyi-Rong Duh                                                                                                                | 380 |

| Striping Cache: A Global Cache for Striped Network File System<br>Sheng-Kai Hung, Yarsun Hsu                                                                                                                   | 387 |

| DTuplesHPC: Distributed Tuple Space for Desktop High Performance<br>Computing                                  | 394 |

|----------------------------------------------------------------------------------------------------------------|-----|

| Yi Jiang, Guangtao Xue, Minglu Li, Jinyuan You                                                                 |     |

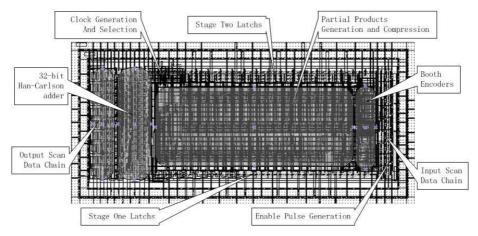

| The Algorithm and Circuit Design of a 400MHz 16-Bit Hybrid                                                     |     |

| Multiplier<br>Zhentao Li, Shuming Chen, Zhaoliang Li, Conghua Lei                                              | 401 |

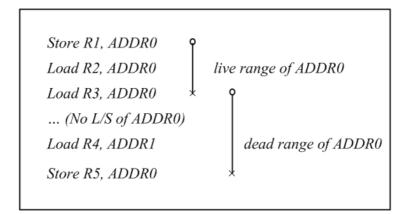

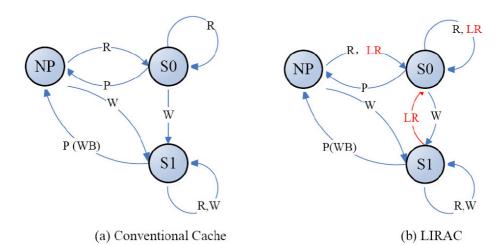

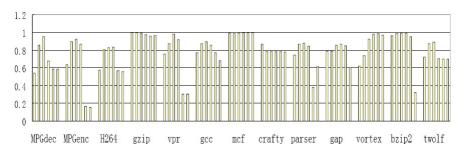

| Live Range Aware Cache Architecture<br>Peng Li, Dongsheng Wang, Songliu Guo, Tao Tian,                         | 409 |

| Weimin Zheng                                                                                                   |     |

| The Challenges of Efficient Code-Generation for Massively Parallel<br>Architectures                            | 416 |

| Jason M. McGuiness, Colin Egan, Bruce Christianson,<br>Guang Gao                                               | 110 |

| Reliable Systolic Computing Through Redundancy<br>Kunio Okuda, Siang Wun Song, Marcos Tatsuo Yamamoto          | 423 |

| A Diversity-Controllable Genetic Algorithm for Optimal Fused Traffic<br>Planning on Sensor Networks            | 430 |

| A Context-Switch Reduction Heuristic for Power-Aware Off-Line<br>Scheduling                                    | 437 |

| Biju Raveendran, Sundar Balasubramaniam, K Durga Prasad,<br>S. Gurunarayanan                                   | 407 |

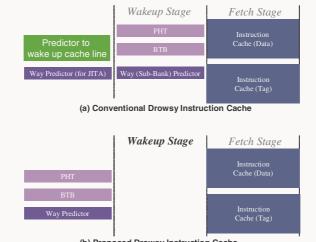

| On the Reliability of Drowsy Instruction Caches<br>Soong Hyun Shin, Sung Woo Chung, Chu Shik Jhon              | 445 |

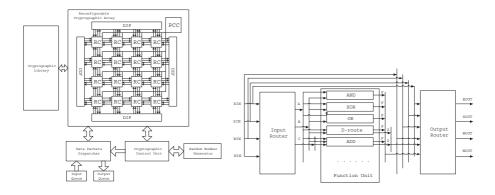

| Design of a Reconfigurable Cryptographic Engine<br>Kang Sun, Lingdi Ping, Jiebing Wang, Zugen Liu, Xuezeng Pan | 452 |

| Enhancing ICOUNT2.8 Fetch Policy with Better Fairness for SMT                                                  |     |

| Processors<br>Caixia Sun, Hongwei Tang, Minxuan Zhang                                                          | 459 |

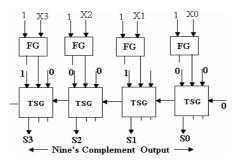

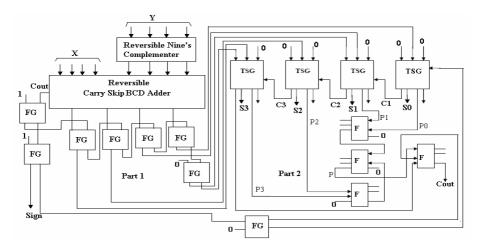

| The New BCD Subtractor and Its Reversible Logic Implementation<br>Himanshu Thapliyal, M.B Srinivas             | 466 |

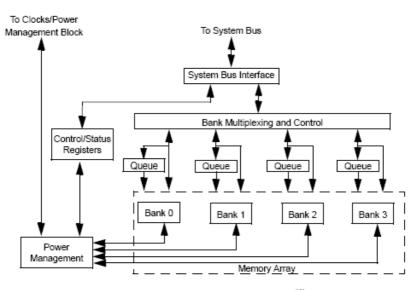

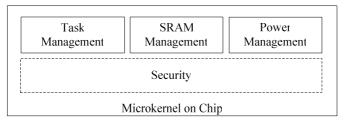

| Power-Efficient Microkernel of Embedded Operating System                                                       | 179 |

| on Chip<br>Tianzhou Chen, Wei Hu, Yi Lian                                                                      | 473 |

| Understanding Prediction Limits Through Unbiased Branches<br>Lucian Vintan, Arpad Gellert, Adrian Florea, Marius Oancea,<br>Colin Egan | 480 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

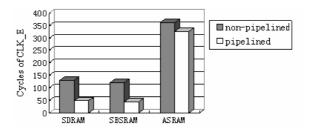

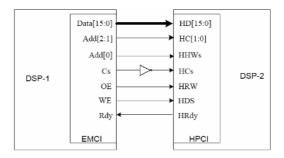

| Bandwidth Optimization of the EMCI for a High Performance<br>32-bit DSP<br>Dong Wang, Xiao Hu, Shuming Chen, Yang Guo                  | 488 |

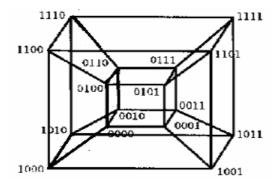

| Research on Petersen Graphs and Hyper-cubes Connected<br>Interconnection Networks<br>Lei Wang, Zhiping Chen                            | 495 |

| Cycle Period Analysis and Optimization of Timed Circuits<br>Lei Wang, Zhi-ying Wang, Kui Dai                                           | 502 |

| Acceleration Techniques for Chip-Multiprocessor Simulator Debug<br>Haixia Wang, Dongsheng Wang, Peng Li                                | 509 |

| A DDL–Based Software Architecture Model<br>Meiling Wang, Lei Liu                                                                       | 516 |

| Branch Behavior Characterization for Multimedia Applications<br>Chia-Lin Yang, Shun-Ying Wang, Yi-Jung Chen                            | 523 |

| Optimization and Evaluating of StreamYGX2 on MASA Stream<br>Processor                                                                  | 531 |

| SecureTorrent: A Security Framework for File Swarming<br>Kenneth Wilson, Philip Machanick                                              | 538 |

| Register Allocation on Stream Processor with Local Register File<br>Nan Wu, Mei Wen, Ju Ren, Yi He, Chunyuan Zhang                     | 545 |

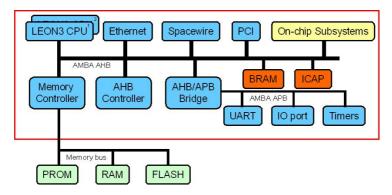

| A Self-reconfigurable System-on-Chip Architecture for Satellite<br>On-Board Computer Maintenance<br>Xiaofeng Wu, Tanya Vladimirova     | 552 |

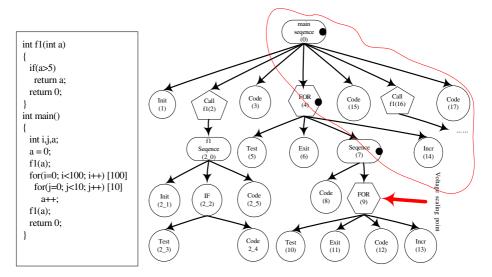

| Compile-Time Thread Distinguishment Algorithm on VIM-Based<br>Architecture                                                             | 559 |

| Designing a Coarse-Grained Reconfigurable Architecture Using Loop<br>Self-Pipelining<br>Jinhui Xu, Guiming Wu, Yong Dou, Yazhuo Dong   | 567 |

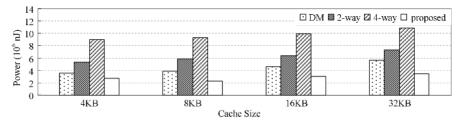

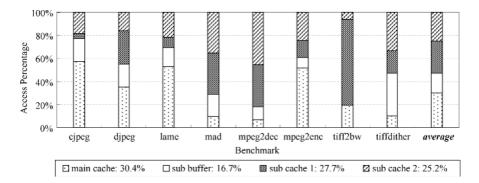

| Low-Power Data Cache Architecture by Address Range Reconfiguration<br>for Multimedia Applications                                                                                    | 574 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

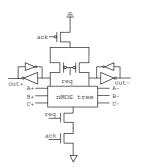

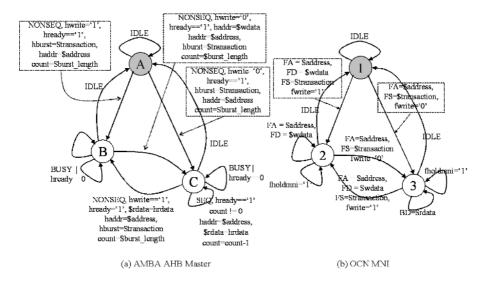

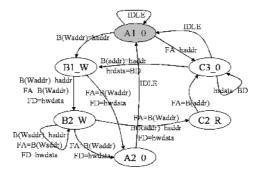

| Automatic Synthesis of Interface Circuits from Simplified IP Interface<br>Protocols                                                                                                  | 581 |

| An Architectural Leakage Power Reduction Method for Instruction<br>Cache in Ultra Deep Submicron Microprocessors<br><i>Chengyi Zhang, Hongwei Zhou, Minxuan Zhang, Zuocheng Xing</i> | 588 |

| An Efficient Approach to Energy Saving in Microcontrollers<br>Wenhong Zhao, Feng Xia                                                                                                 | 595 |

| Author Index                                                                                                                                                                         | 603 |

## The Era of Multi-core Chips -A Fresh Look on Software Challenges

Guang R. Gao

Endowed Distinguished Professor Dept. of Electrical and Computer Engineering University of Delaware ggao@caps1.ude1.edu

**Abstract.** In the past few months, the world has witnessed the impressive pace that the microprocessor chip vendors' switching to multi-core chip technology. However, this is preventing steep software challenges – both in the migration of application software and in the adaptation of system software.

In this talk, we discuss the challenges as well as opportunities facing software technology in the era of the emerging multi-core chips. We review the software effort failures and lessons learned during the booming years on parallel computing – in the 80s and early 90s, and analyze the issues and challenges today when we are once more trying to explore large-scale parallelism on multi-core chips and systems. We then predict major technology innovations that should be made in order to assure a success this time.

This talk will begin with a discussion based on our own experience on working with fine-grain multithreading from execution/architecture models, system software technology, and relevant application software studies in the past decade. We then outline our recent experience in working on software issues for the next generation multi-core chip architectures. We will present a case study on a mapping of OpenMP on two representative classes of future multi-core architecture models. We discuss several fundamental performance issues facing system software designers.

## Streaming Networks for Coordinating Data-Parallel Programs (Position Statement)

Alex Shafarenko

Compiler Technology and Computer Architecture Group, University of Hertfordshire, United Kingdom A.Shafarenko@herts.ac.uk

**Abstract.** A new coordination language for distributed data-parallel programs is presented, call SNet. The intention of SNet is to introduce advanced structuring techniques into a coordination language: stream processing and various forms of subtyping. The talk will present the organisation of SNet, its major type inferencing algorithms and will briefly discuss the current state of implementation and possible applications.

Process concurrency is difficult to deal with in the framework of a programming language. If properly integrated into the language semantics, it complicates and often completely destroys the properties that enable the kind of profound optimisations that make compilation of computational programs so efficient. One solution to this problem, which is the solution that this talk will present, is the use of so-called coordination languages. A coordination language uses a readilyavailable computation language as a basis, and extends it with a certain communication/synchronisation mechanism thus allowing a distributed program to be written in a purely extensional manner. The first coordination language proposed was Linda[Gel85, GC92], which extended C with a few primitives that looked like function calls and could even be implemented directly as such. However an advanced implementation of Linda would involve program analysis and transformation in order to optimise communication and synchronisation patterns beyond the obvious semantics of the primitives. Further coordination languages have been proposed, many on them extensional in the same way, some not; for the state of the art, see a survey in [PA98] and the latest Coordination conference [JP05].

The emphasis of coordination languages is usually on event management, while the data aspect of distributed computations is not ordinarily focused on. This has a disadvantage in that the structuring aspect, software reuse and component technology are not primary goals of coordination. It is our contention that structuring is key in making coordination-based distributed programming practically useful. In this talk we describe several structuring solutions, which have been laid in the foundation of the coordination language SNet. The language was introduced as a concept in [Sha03]; the complete definition, including semantics and the type system, is available as a technical report [Sha06].

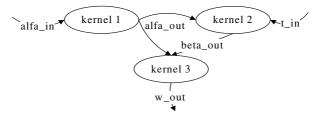

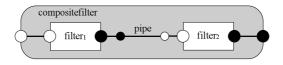

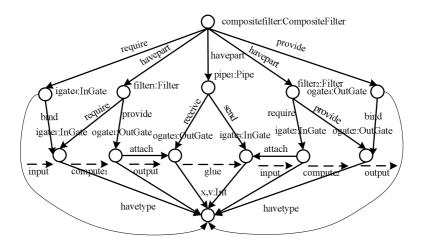

The approach proposed in SNet is based on streaming networks. The application as a whole is represented as a set of self-contained components, called

C. Jesshope and C. Egan (Eds.): ACSAC 2006, LNCS 4186, pp. 2–5, 2006.

"boxes" (SNetis not extensional) written in a data-parallel language. SNet deals with boxes by combining them into networks which can be encapsulated as further boxes. The structuring instruments used are as follows:

- Streams. Instead of arbitrary communication, data is packaged into typed variant records that flow in a sequence from their producer to a single consumer.

- Single-Input, Single-Output(SISO) box and network configuration. Multiple connections are, of course, possible and necessary. The unique feature of SNet is that the multiplicity of connection is handled by SNet combinators so that a box sees a single stream of records coming in. The records are properly attributed to their sources by using types (which include algebraic types, or tagged, disjoint unions). Similarly, the production of a single stream of typed records by a box does not preclude the output separation into several streams according to the type outside the box perimeter.

- Network construction using structural combinators. The network is presented as an expression in the algebra of four major combinators (and a small variety of ancillary constructs): serial (pipelined) composition, parallel composition, infinite serial replication (closure) and infinite parallel replication (called index splitter, as the input is split between the replicas according to an "index" contained in data records). We will show that this small nomenclature of tools is sufficient to construct an arbitrary streaming network.

- Record subtyping. Data streams consist of flat records, whose fields are drawn from a linear hierarchy of array subtypes[Sha02, SS04]. The records as wholes are subtyped since the boxes accept records with extra fields and allow the producer to supply fewer variants than the consumer has the ability to recognise.

- Flow inheritance. Due to subtyping, the boxes may receive more fields in a record than they recognise. In such circumstances flow inheritance causes the extra fields to be saved and then appended to all output records produced in response to a given input one<sup>1</sup>. Flow inheritance enables very flexible pipelining since, on the one hand, a component does not need to be aware of the exact composition of data records that it receives as long as it receives sufficient fields for the processing it is supposed to do; and on the other, the extra data are not lost but passed further down the pipeline that the components may be connected by.

- Record synchronizers. These are similar to I-structures known from dataflow programming. SNet synchronisers are typed SISO boxes that expect two records of certain types and produce a joint record. No other synchronisation mechanism exists in SNet, and no synchronisation capability is required of the user-defined boxes.

- The concept of network feedback in the form of a closure operator. This connects replicas of a box in a (conceptually) infinite chain, with the input

<sup>&</sup>lt;sup>1</sup> This is a conceptual view; in practice the data fields are routed directly to their consumers, thanks to the complete inferability of type in SNet.

data flowing to the head of the chain and the output data being extracted on the basis of fixed-point recognition. The main innovation here is the proposal of a type-defined fixed point (using flow inheritance as a statically recognisable mechanism), and the provision of an efficient type-inference algorithm. As a result, SNet has no named channels (in fact, no explicit channels at all) and the whole network can be defined as a single expression in a certain combinator algebra.

The talk will address the following issues. We will first give an overview of stream processing pointing out the history of early advances [Kah74, AW77, HCRP91], the semantic theory [BS01] and the recent languages [Mic02]. Then the concepts of SNet will be introduced, focusing in turn on: overall organisation and combinators, type system and inference algorithms, concurrency and synchronisation, and the binding for a box language. Finally a sketch of a complete application in the area of plasma simulation using the particle-in-cell method will be provided.

Work is currently underway to implement SNet as a coordination language for a large EU-sponsored Integrated Project named "EATHER" [Pro], which is part of the Framework VI Advanced Computing Architecture Initiative. University of Hertfordshire is coordinating the software side of the project; if time permits, the talk will touch upon the progress achieved to date.

#### References

| [AW77]   | E. A. Ashcroft and W. W. Wadge. Lucid, a nonprocedural language with       |

|----------|----------------------------------------------------------------------------|

|          | iteration. Communications of the ACM, 20(7):519–526, 1977.                 |

| [BS01]   | M Broy and G Stefanescu. The algebra of stream processing functions.       |

|          | Theoretical Computer Science, (258):99–129, 2001.                          |

| [GC92]   | D Gelernter and N Carriero. Coordination languages and their significance. |

|          | Communications of the ACM, 35(2):96–107, Feb. 1992.                        |

| [Gel 85] | David Gelernter. Generative communication in linda. ACM Trans Pro-         |

|          | gram. Lang Syst., 1(7):80–112, 1985.                                       |

| [HCRP91] | N. Halbwachs, P. Caspi, P. Raymond, and D. Pilaud. The synchronous         |

|          | data-flow programming language LUSTRE. Proceedings of the IEEE,            |

|          | 79(9):1305–1320, September 1991.                                           |

| [JP05]   | Jean-Marie Jacquet and Gian Pietro Picco, editors. Coordination Mod-       |

|          | els and Languages. 7th International Conference, COORDINATION 2005,        |

|          | Namur, Belgium, April 20-23, 2005, volume 3454 of Proceedings Series:      |

|          | Lecture Notes in Computer Science, Vol. 3454 Jacquet, Jean-Marie; Picco,   |

|          | Gian Pietro (Eds.) 2005, X, 299 p., Softcover Lecture Notes in Computer    |

|          | Science. Springer Verlag, 2005.                                            |

| [Kah74]  | G Kahn. The semantics of a simple language for parallel programming. In    |

|          | L Rosenfeld, editor, Information Processing 74, Proc. IFIP Congress 74.    |

|          | August 5-10, Stockholm, Sweden, pages 471–475. North-Holland, 1974.        |

| [Mic02]  | Michael I. Gordon et al. A stream compiler for communication-exposed       |

|          | architectures. In Proceedings of the Tenth International Conference on     |

|          | Architectural Support for Programming Languages and Operating Systems,     |

|          | San Jose, CA. October 2002, 2002.                                          |

- [PA98] G A Papadopoulos and F Arbab. Coordination models and languages. In Advances in Computers, volume 46. Academic Press, 1998.

- [Pro] The AETHER Project. http://aetherist.free.fr/Joomla/index.php.

- [Sha02] Alex Shafarenko. Coercion as homomorphism: type inference in a system with subtyping and overloading. In PPDP '02: Proceedings of the 4th ACM SIGPLAN international conference on Principles and practice of declarative programming, pages 14–25, 2002.

- [Sha03] Alex Shafarenko. Stream processing on the grid: an array stream transforming language. In *SNPD*, pages 268–276, 2003.

- [Sha06] Alex Shafarenko. Snet: definition and the main algorithms. Technical report, Department of Computer Science, 2006.

- [SS04] Alex Shafarenko and Sven-Bodo Scholz. General homomorphic overloading. In Implementation and Application of Functional Languages. 16th International Workshop, IFL 2004, Lübeck, Germany, September 2004. Revised Selected Papers., LNCS'3474, pages 195–210. Springer Verlag, 2004.

## Implementations of Square-Root and Exponential Functions for Large FPGAs

Mariusz Bajger<sup>1</sup> and Amos R. Omondi<sup>2</sup>

<sup>1</sup> School of Informatics and Engineering Flinders University, Bedford Park, SA 5042, Australia

<sup>2</sup> School of Electrical and Electronic Engineering Yonsei University, Seoul, Korea

Mariusz.Bajger@flinders.edu.au, amos@yonsei.ac.kr

Abstract. This paper discusses low-error, high-speed evaluation of two elementary functions: square-root (which is required in IEEE-754 standard on computer arithmetic) and exponential (which is common in scientific calculations). The basis of the proposed implementations is piecewise-linear interpolation but with the constants chosen in a way that minimizes relative error. We show that by placing certain constraints on the errors at three points within each interpolation interval, relative errors are greatly reduced. The implementation-targets are large FPGAs that have in-built multipliers, adders, and distributed memory.

#### 1 Introduction

Many techniques exist for evaluating elementary functions: polynomial approximations, CORDIC algorithms, rational approximations, table-driven methods, and so forth [1], [2]. For hardware implementation, accuracy, performance and cost are all important. The latter two mean that many of the better techniques that have been developed in numerical analysis (and implemented in software) are not suitable for hardware implementation. CORDIC is perhaps the most studied technique for hardware implementation. Its primary merits are that the same hardware can be used for several functions, but, because of its iterative nature, its performance is rather poor. High-order polynomial approximations can give low-error implementations, but are generally not suitable for hardware implementation, because of the number of arithmetic operations (multiplications and additions) that must be performed for each value; either much hardware must be used, or performance be compromised. And a similar remark applies to pure table-driven methods, unless the tables are quite small: large tables will be both slow and costly. The practical implication of these constraints is that many of the better techniques that have been developed in numerical analysis, and which are easily implemented in software, are not suitable for hardware implementation.

C. Jesshope and C. Egan (Eds.): ACSAC 2006, LNCS 4186, pp. 6–23, 2006.

Given trends in technology, it is apparent that at present the best technique for hardware function-evaluation is a combination of low-order polynomials and small look-up tables. This is the case for both ASIC and FPGA technologies, especially for the latter, in which current large devices (such as the Xilinx Virtex [5], [6]) are equipped with substantial amounts of distributed memory as well as many arithmetic units (notably mulipliers and adders).<sup>1</sup> The combination of low-order polynomials (primarily linear ones) is not new – the main challenges has always been one of how to choose the best interpolation points and how to ensure that look-up tables remain small.

For most elementary functions, interpolation with uniformly-sized intervals (i.e. uniformly-spaced abscissae) is not ideal. Nevertheless, for hardware implementation, the need to quickly map arguments onto the appropriate intervals dictates the use of such intervals. With this choice and linear interpolation, the critical issue then becomes that of what function-value to associate with each interval. The most common choice has been to arbitrarily select the value at the midpoint of the interval — that is, if  $x \in [L, U]$ , then f(x) = f((L+U)/2) — or to choose a value that minimizes absolute errors.<sup>2</sup> Neither is particularly good: as we shall show, even with a fixed number of intervals, the best function-value for an interval is generally not the midpoint. And, depending on the "curvature" of the function at hand, relative error may be more critical than absolute error. For the functions we consider, the effect of a given value of absolute error is not constant or linear, and therefore the relative error is more critical than the absolute error.

The rest of the paper is organized as follows. Section 2 gives a brief overview of the Xilinx Virtex-4 FPGA. Section 3 outlines the general approach that we use in the function approximation, and the next two sections, the main parts of the paper, correspond to each of the two functions. Section 5 is a discussion of the results we obtained. And Section 6 is a concluding summary.

#### 2 Xilinx Virtex-4 FPGA

As indicated above, our primary target is large FPGAs. The structure of such devices makes them particularly well suited to low-order polynomial approximations: the devices have in-built (and reasonably wide) adders and multipliers, as well as relatively large amounts of memory. Moreover, the arrangement of the arithmetic units is eminently suited to the multiply-then-add sequence that is required in polynomial approximations. In this section, we shall briefly give the details of a current FPGA device, the Xilinx Virtex-4, that is typical of such state-of-the-art FPGA devices. We also indicate how its structure is well-suited to piecewise-linear interpolation.

<sup>&</sup>lt;sup>1</sup> This is validated by a recent study of FPGA implementations of various techniques [3].

$<sup>^{2}</sup>$  Following [4], we use *absolute error* to refer to the difference between the exact value and its approximation; that is, it is not the absolute value of that difference.

Fig. 1. DSP48 tile of Xilinx Virtex-4

The Virtex-4 is actually a family of devices with many common features but with variations in speed, logic-capacity, and so forth. A Virtex-4 device consists of an array of up to  $192 \times 116$  tiles (in generic FPGA terms, two tiles form a CLB), up to 1392 Kb of *Distributed-RAM*, up to 9936 Kb of *Block-RAM* (arranged in 18-Kb blocks), up to 2 PowerPC 405 processors, up to 512 Xtreme DSP slices for arithmetic, several Input/Ouput blocks, and so forth [18, 19]. There are currently 17 devices in the family:

- eight LX devices, optimized for logic intensive applications;

- three SX devices, optimized for embedded applications; and

- six FX devices, optimized for digital-signal-processing applications.

Table 1 gives the parameters for typical members (the largest) of each class. Observe that many neural-network computations are DSP-like, and, therefore, the FX class may be taken as the ideal target.

|           | Logic  | Distr.   | XDSP   | Block    | Power         |

|-----------|--------|----------|--------|----------|---------------|

| Device    | Slices | RAM (Kb) | Slices | RAM (Kb) | $\mathbf{PC}$ |

| XC4VLX200 |        |          | 96     | 6,048    | 0             |

| XC4VSX55  |        |          | 512    | 5,760    | 0             |

| XC4VFX140 | 63,168 | 987      | 192    | 9,936    | 2             |

Table 1. Xilinx Virtex-4 devices

A tile is made of two Xtreme DSP48 slices that together consist of eight function-generators (configured as 4-bit lookup tables capable of realizing any four-input boolean function), eight flip-flops, two fast carry-chains, 64 bits of Distributed-RAM, and 64-bits of shift register. There are two types of slices: SLICEM, which consists of logic, Distributed RAM, and shift registers, and SLICEL, which consists of logic only. Figure 3 shows the basic elements of a tile. (For ease of visual presentation, we have not shown the memory elements.) Since the approximation scheme we use is based on linear interpolation, Distributed RAM is not suitable for the storage of the required constants, unless there is only a small number of such constants and they are of low precision. Block RAM should therefore be used for such storage.

Blocks of the Block-RAM are true dual-ported and are recofigurable to various widths and depths (from  $16K \times 1$  to  $512 \times 36$ ); this memory lies outside the slices but operates at the same high speed. Distributed RAM is located inside the slices and is nominally single-port but can be configured for dual-port operation. The PowerPC processor core is of 32-bit Harvard architecture, implemented as a 5-stage pipeline. The significance of this last unit is in relation to the serial parts of even highly parallel applications — one cannot live by parallelism alone. The maximum clock rate for all of the units above is 500 MHz.

Arithmetic functions in the Virtex-4 fall into one of two main categories: arithmetic within a tile and arithmetic within a collection of slices; the latter is necessary for high-precision computations. All the slices together make up what is called the *XtremeDSP*. DSP48 slices are optimized for multipliy, add, and mutiply-add operations. There are 512 DSP48 slices in the largest Virtex-4 device, organized in two-slice tiles (Figure 1). Each slice consists primarily of an 18-bit×18-bit multiplier (with sign-extension of the result to 48 bits), a 48-bit adder/subtractor, multiplexers, registers, and so forth. Given the importance of inner-product computations. With 512 DSP48 slices operating at a peak rate of 500 MHz, a maximum performance of 256 Giga-MACs (multiply-accumlate operations) per second is possible. (As an aside, observe that this is well beyond anything that has so far been offered by way of a custom ASIC neurocomputer.)

The scheme we describe below is based on piecewise linear interpolation; that is, the basic approximation function is  $\hat{f} = c_1 + c_2 x$ , for some constants  $c_1$  and  $c_2$ . So the structure of Figure 1 is naturally suitable. Also, while it might appear that for low-precision outputs, and given the relatively large amounts of memory in the Virtex-4, a pure table-lookup approach might be better, that is not so: That might be an important consideration in ASIC technology, because it eliminates the need for a multiplier and an adder, but there is no advantage gained if these arithmetic units are already available. We shall below return briefly to this point.

#### 3 Basic Approach

The general approach we take is as follows. Let I = [L, U] be a real interval with L < U and let  $f: I \to \mathbf{R}$  be a function to be approximated (where  $\mathbf{R}$  denotes the set of real numbers). Suppose that  $\hat{f}: I \to \mathbf{R}$  is a linear function — that is,  $\hat{f}(x) = c_1 + c_2 x$ , for some constants  $c_1$  and  $c_2$  — that approximates f. Our objective is to investigate the relative-error function

$$\varepsilon(x) = \frac{f(x) - \hat{f}(x)}{f(x)}, \quad x \in I,$$

(1)

and to find  $c_1$  and  $c_2$  such that  $\varepsilon(x)$  is small. One way to obtain reasonably good values for  $c_1, c_2$  is to impose the condition

$$f(L) = \widehat{f}(L), \quad f(U) = \widehat{f}(U)$$

(C)

to calculate  $c_1$  and  $c_2$ . As we shall show, a much better result can be obtained using the "improved" condition

$$|\varepsilon(L)| = |\varepsilon(U)| = |\varepsilon(x_{stat})|, \qquad (IC)$$

where  $x_{stat}$  (stationary point) is the value of x for which  $\varepsilon(x)$  has a local extremum.

An example of the use of this technique to approximate reciprocals can be found in [2], the approximation of the reciprocal function. (The second and third columns of Tables 1 and 2 show the differences between the direct reduction of the relative error, i.e. our approach, and reduction of the relative error via reduction in the absolute error.) We will study each of the three functions seperately and in each case show that, compared with the results from using the condition (C), the improved condition (IC) yields a massive 50% reduction in the magnitude of the relative error. In each case we shall also give the analytical formulae for the constants  $c_1$  and  $c_2$ .

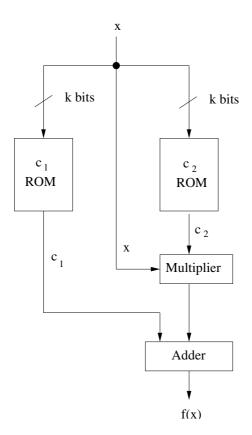

It is well-known that by using more than two data points one can get better approximation; that is, by subdividing the main interval for interpolation into several subintervals and keeping to a minimum the error on each of the subintervals yields to a better accuracy of approximation for the given function. Since for computer-hardware implementations it is convenient that the number of data points be a power of two, we will assume that the interval I = [L, U] is divided into  $2^k$  intervals:  $[L, L + \Delta/2^k)$ ,  $[L + \Delta/2^k, L + 2\Delta/2^k]$ ,...,  $[L + (2^k - 1)\Delta/2^k, U]$ , where  $\Delta$  denotes the difference U - L. Then, given an argument, x, the interval into which it falls can be located readily by using, as an address, the k most significant bits of the binary representation of x. The proposed hardware implementation therefore has the high-level organization shown in Fig. 2. The two look-up tables (ROMs, or RAMs in the case of FPGAs) hold the constants  $c_1$  and  $c_2$  for each interval.

Fig. 2. Hardware organization for function evaluation

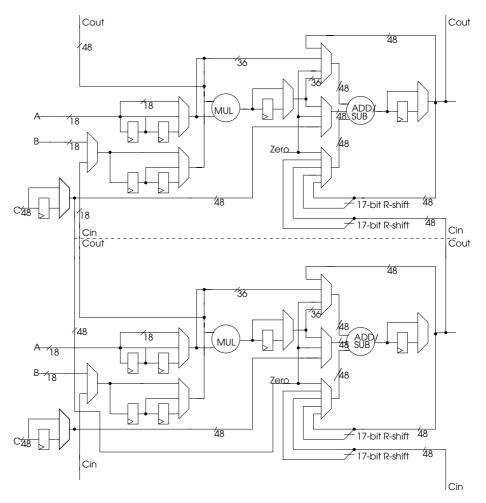

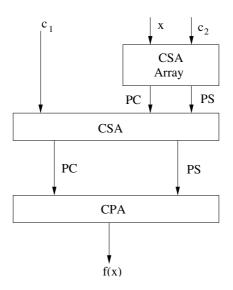

For a high-speed implementation, the actual structure may differ in several ways. Consider for example the Multiplier-Adder pair. Taken individually, the adder must be a carry-propagate adder (CPA); and the multiplier, if it is of high performance will consist of an array of carry-save adders (CSAs) with a final CPA to assimilate the partial-sum/partial-carry (PC/PS) output of the CSAs.

Now, the multiplier-CPA may be replaced with two CSAs, to yield much higher performance. Therefore, in a high speed implementation the actual structure would have the form shown in Fig. 3. It should be noted, though, that this new oraganization may not be the best one for the sort of FPGAs that we envisage, because the in-built structure of FPGAs impose certain constraints.

Fig. 3. High-performance hardware organization for function evaluation

Throughout the paper we shall illustrate our results with detailed numerical data obtained for a fixed number of intervals. All numerical computations, were done with the computer algebra system MAPLE [8] for the interval I = [0.5, 1] and k = 4; that is, I was divided into 16 intervals:

$$\left[\frac{1}{2}, \frac{17}{32}, \frac{9}{16}, \frac{19}{32}, \frac{5}{8}, \dots, 1\right].$$

(Note that evaluation on any other interval can be transformed into evaluation on the interval [0.5, 1].) We have also used MAPLE to perform many of complex symbolic computations required throughout the paper.

Floating-point calculations in MAPLE are carried out in finite precision, with intermediate results rounded to a precision that is specified by MAPLE constant Digits. This constant controls the number of digits MAPLE uses for calculations. Thus, generally, the higher the Digits value is, the higher accuracy of the obtainable results, with roundoff errors as small as possible. We set Digits value to 35 for numerical computations. Numerical results will be presented using standard decimal scientific notation.

#### 4 The Square-Root Function

Let  $f: I \to \mathbf{R}$ ,  $f(x) = \sqrt{x}$ , and  $\hat{f}: I \to \mathbf{R}$ ,  $\hat{f}(x) = c_1 + c_2 x$ , where  $c_1, c_2$  are constants. By condition (C) we get the system

$$\begin{cases} c_1 + c_2 L = \sqrt{L}, \\ c_1 + c_2 U = \sqrt{U}, \end{cases}$$

which has the solution

$$c_1 = \frac{-U\sqrt{L} + \sqrt{UL}}{\frac{-U+L}{\sqrt{U} + \sqrt{L}}},$$

$$c_2 = \frac{-\sqrt{U} + \sqrt{L}}{-U+L}.$$

Hence,  $\hat{f}$  may be written as

$$\widehat{f}(x) = \frac{-U\sqrt{L} + \sqrt{U}L - x\left(\sqrt{U} - \sqrt{L}\right)}{-U + L}, \quad x \in I.$$

Substituting the above into (1) and simplifying, we obtain the formula for the relative error on the interval I = [L, U]:

$$\varepsilon(x) = 1 + \frac{U\sqrt{L} - \sqrt{U}L + x\left(\sqrt{U} - \sqrt{L}\right)}{(-U+L)\sqrt{x}},$$

of which the first derivative with respect to x is

$$\varepsilon'(x) = \frac{x\sqrt{U} - x\sqrt{L} - U\sqrt{L} + \sqrt{U}L}{2x^{3/2}(-U+L)}.$$

By solving the equation  $\varepsilon'(x) = 0$ , we get the unique stationary point

$$x_{stat} = \sqrt{UL}.$$

If we now take the second derivative of the error function

$$\varepsilon''(x) = \frac{x\sqrt{U} - x\sqrt{L} - 3U\sqrt{L} + 3\sqrt{U}L}{4x^{5/2}(-U+L)},$$

substitute  $x_{stat}$  into this formula, and simplify, we obtain

$$\varepsilon''(x_{stat}) = \frac{U\sqrt{L} - \sqrt{U}L}{2(-U+L)LU\sqrt{\sqrt{UL}}}.$$

Since U > L, the second derivative is negative at  $x_{stat}$ , which means that the relative error has a maximum value at this point. Moreover, by condition (C),  $\varepsilon$  vanishes at the end points of I, so it is in fact an absolute maximum. With this extremum value for the error function, it makes sense to consider an (IC)-type

of condition, in which we equalize errors at the end-point and the error at the point of maximum-error amplitude.

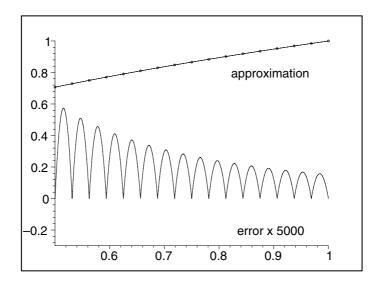

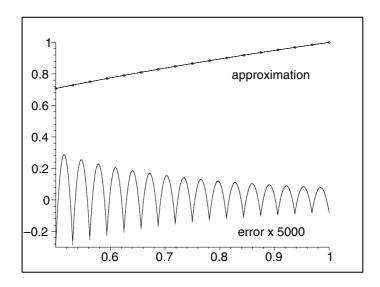

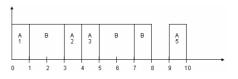

For the 16-interval example, application of the condition (C) gives the results shown in Fig. 4, of the approximation plots together with the corresponding graph of the error function.

Fig. 4. Piecewise-linear approximation of the square-root function

Note, that the maximum value for error occurs on the first interval and is

$$\varepsilon_{max} = 1.148435e - 04,$$

(2)

which corresponds, approximately, to 0.57 on our (magnified) graph. We will later compare this number with the corresponding value obtained using our improved approximation.

We next derive an improved error-formula based on the condition (IC). The first equation in condition (IC) gives

$$\frac{\sqrt{U} - c_1 - c_2 U}{\sqrt{U}} = \frac{\sqrt{L} - c_1 - c_2 L}{\sqrt{L}},$$

whence

$$c_2 = \frac{c1\left(\sqrt{L} - \sqrt{U}\right)}{-\sqrt{L}U + \sqrt{U}L} = \frac{c_1}{\sqrt{UL}}.$$

(3)

Consequently, by (1), we get

$$\varepsilon(x) = 1 - \frac{c_1}{\sqrt{x}} - \frac{c_1\sqrt{x}}{\sqrt{UL}} \tag{4}$$

and, taking the first and second derivative,

$$\varepsilon'(x) = \frac{c_1\left(\sqrt{UL} - x\right)}{2x^{3/2}\sqrt{UL}}$$

and  $\varepsilon''(x) = \frac{c_1\left(x - 3\sqrt{UL}\right)}{4x^{5/2}\sqrt{UL}}$ ,

for  $x \in I$ . Solving  $\varepsilon'(x) = 0$ , gives  $x_{stat} = \sqrt{UL}$ , and substituting  $x_{stat}$  into the second derivative formula yields

$$\varepsilon''(x_{stat}) = \frac{-c_1}{2UL\sqrt{\sqrt{UL}}}$$

Since  $c_1$  is positive (f(0) > 0 and f is increasing), from the last equation, we may infer that the second derivative is negative at  $x_{stat}$ , which means that the error attains maximum at this point. It is a simple matter to check that it is in fact an absolute maximum. By (1), we may now write

$$\varepsilon(x_{stat}) = 1 - \frac{c_1}{\sqrt{x_{stat}}} - \frac{c_1\sqrt{x_{stat}}}{\sqrt{UL}} = 1 - \frac{2c_1}{\sqrt{x_{stat}}},\tag{5}$$

since  $x_{stat} = \sqrt{UL}$ .

Observe that from condition (IC), we have

$$\varepsilon(L) = -\varepsilon(x_{stat}).$$

That is, by (4) and (5),

$$1 - \frac{c_1}{\sqrt{L}} - \frac{c_1}{\sqrt{U}} = -1 + \frac{2c_1}{\sqrt{x_{stat}}},$$

whence

$$c_1 = \frac{2x_{stat}}{2\sqrt{x_{stat}} + \sqrt{U} + \sqrt{L}},$$

and, by (3),

$$c_2 = \frac{2}{2\sqrt{x_{stat}} + \sqrt{U} + \sqrt{L}}.$$

Therefore

$$\widehat{f}(x) = \frac{2(x_{stat} + x)}{2\sqrt{x_{stat}} + \sqrt{U} + \sqrt{L}}, \quad x \in I.$$

Finally, (1) gives the following improved formula for the relative error on interval I

$$\varepsilon(x) = 1 - \frac{\sqrt{x_{stat} + x}}{\left(2\sqrt{x_{stat}} + \sqrt{U} + \sqrt{L}\right)\sqrt{x}}$$

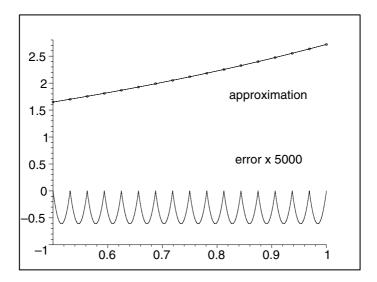

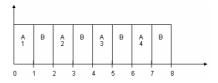

Figure 5 gives the graphs for the new approximation and the corresponding relative error on the sixteen intervals.

Fig. 5. Improved piecewise-linear approximation of the square-root function

The maximum value for relative error is now

$$\varepsilon_{max} = 5.742506e - 05,$$

which corresponds approximately to 0.29 on the "magnified" graph. MAPLE ensures us that this value is in fact the global maximum of the error-magnitude. (We omit the tedious and rather long, but elementary, proof of this fact for the general case). In fact, the maximum magnitude for the left-end is 5.74249902e - 05, and for the right-end it is 5.74245863e - 05.

To conclude the section, we compare the current maximum value to our previous error estimation given by (2). An easy computation shows that the magnitude of the maximum relative-error decreased by 50.00279 percent. There is one further additional point that should be noted regarding the new approximation: observe that in Fig. 4 all the errors are of the same sign, i.e. positive. This means that in a sequence of square-root evaluations, the total error will be cumulative. On the other hand, in Fig. 5 there are changes of sign, which means that there will be some cancellation. Note that this is precisely the reason why in the mandated rounding method in IEEE-754 (i.e. round-to-nearest), boundary cases are alternately rounded up or down, according to the least significant bit of the number being rounded.

#### 5 The Exponential Function

In this section we consider  $f: I \to \mathbf{R}$ , where  $f(x) = e^x$  and, as in the preceding section, we will look for a linear function  $\hat{f}: I \to \mathbf{R}$ , where  $\hat{f}(x) = c_1 + c_2 x$ , such that  $\varepsilon(x)$ , given by (1), is small.

We begin by an analysis based on a natural assumption expressed by condition (C): the error should vanish at both end-points of the considered interval. This is expressed by the following pair of equations, with  $c_1$ ,  $c_2$  as unknown variables

$$\begin{cases} c_1 + c_2 L = e^L, \\ c_1 + c_2 U = e^U. \end{cases}$$

A routine algebraic calculation gives

$$c_1 = \frac{-Ue^L + e^U L}{-U + L}$$

and  $c_2 = \frac{-e^U + e^L}{-U + L}$ .

Now, the function  $\widehat{f}$  may be expressed as

$$\widehat{f}(x) = \frac{-Ue^L + e^U L - xe^U + xe^L}{-U + L}, \quad x \in I,$$

and the relative error on I is then

$$\varepsilon(x) = \frac{\left(-e^x U + e^x L + U e^L - e^U L + x e^U - x e^L\right) e^{-x}}{-U + L}$$

Differentiating  $\varepsilon(x)$  twice, with respect to x, gives

$$\varepsilon'(x) = \frac{e^{-x} \left( e^U - e^L - Ue^L + e^U L - xe^U + xe^L \right)}{-U + L}, \quad x \in I,$$

and

$$\varepsilon''(x) = \frac{e^{-x} \left(-Ue^L + e^U L - xe^U + xe^L\right)}{-U + L}, \quad x \in I.$$

Solving  $\varepsilon'(x) = 0$ , we find that the only stationary point is

$$x_{stat} = \frac{-e^{U} + e^{L} + Ue^{L} - e^{U}L}{-e^{U} + e^{L}}.$$

To check for local extremum, we investigate the sign of the second derivative at this point. Performing elementary algebraic computations, we derive the formula

$$\varepsilon''(x_{stat}) = \frac{e^{\alpha} \left(-e^{U} + e^{L}\right)}{-U + L},$$

where, for simplicity of notation, we have used  $\alpha$  to denote the value

$$\frac{-e^U + e^L + Ue^L - e^U L}{-e^U + e^L}.$$

(6)

Since  $e^{\alpha}$  is positive and the exponential is an increasing function, we may infer that  $\varepsilon''(x_{stat})$  is positive, which means that the magnitude of the relative error has a maximum at this point. It suggests, as in the case of square-root function,

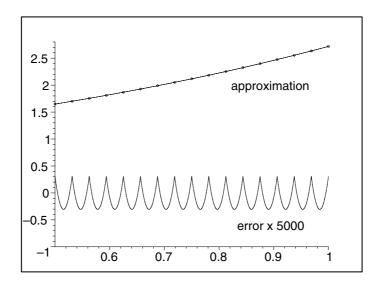

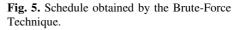

that a better error approximation can be obtained if we try to bound the error at this point. Figure 6 shows the approximation and the corresponding relativeerror for the 16-interval case. The maximum amplitude of the error is

$$\varepsilon_{max} = 1.220761e - 04\tag{7}$$

which translates approximately to 0.61 on our "magnified" graph.

Fig. 6. Piecewise-linear approximation of the exponential function

We next show that condition (IC) yields a much better error approximation. The following equality, which follows immediately from (6), will be useful in the sequel

$$1 - \alpha = \frac{-e^L U + e^U L}{e^L - e^U}.$$

(8)

Observe that the relative error is now

$$\varepsilon(x) = \frac{e^x - c_1 - c_2 x}{e^x}, \qquad x \in I.$$

(9)

Comparying  $\varepsilon(L)$  and  $\varepsilon(U)$  gives

$$\frac{e^U - c_1 - c_2 U}{e^U} = \frac{e^L - c_1 - c_2 L}{e^L}.$$

Hence, using (6),

$$c_2 = \frac{c_1 \left( e^L - e^U \right)}{-e^L U + e^U L} = \frac{c_1}{1 - \alpha}.$$

(10)

Substituting for  $c_2$  into (9) we obtain

$$\varepsilon(x) = \frac{e^x - c_1 - \frac{c_1}{1 - \alpha}x}{e^x}, \quad x \in I,$$

(11)

and differentiation with respect to x yields

$$\varepsilon'(x) = c_1 e^{-x} \left[ 1 - \frac{1}{1 - \alpha} (1 - x) \right] = c_1 e^{-x} \left[ \frac{x - \alpha}{1 - \alpha} \right], \quad x \in I.$$

(12)

Thus,  $\varepsilon'(x) = 0$  iff  $x = \alpha$  (since  $e^{-x} > 0$  and  $c_1 > 0$ ); that is,  $\alpha$  is the only stationary point for  $\varepsilon$ .

We now need to check the sign of the second derivative at this point in order to ensure that it is a local extremum. Let us take the second derivative of the error function and apply (8):

$$\varepsilon''(x) = \frac{c_1}{1 - \alpha} \left[ -e^{-x}x + e^{-x} + \alpha e^{-x} \right] = \frac{c_1 e^{-x}}{1 - \alpha} \left( -x + 1 + \alpha \right), \quad x \in I$$

Hence

$$\varepsilon''(\alpha) = c_1 \frac{e^{-\alpha}}{1-\alpha}.$$

This clearly shows that the second derivative is positive at this point, and, therefore, that  $\alpha$  is a local minimum for  $\varepsilon$ .

We now turn to (11), which gives

$$\varepsilon(\alpha) = \frac{e^{\alpha} - c_1 - \frac{c_1 \alpha}{1 - \alpha}}{e^{\alpha}},$$

$$\varepsilon(L) = \frac{e^L - c_1 - \frac{c_1}{1 - \alpha}L}{e^L}.$$

From condition (IC), we have, in particular,  $\varepsilon(L) = -\varepsilon(\alpha)$ ; that is,

$$\frac{e^{\alpha}-c_1-\frac{c_1\alpha}{1-\alpha}}{e^{\alpha}}=\frac{-e^L+c_1+\frac{c_1}{1-\alpha}L}{e^L}.$$

Whence, by (8),

$$c_{1} = \frac{2e^{\alpha}(1-\alpha)\left(-e^{U}+e^{L}\right)}{-e^{U}+e^{L}-e^{\alpha}(U-L)},$$

and by (10),

$$c_2 = \frac{2e^{\alpha} \left(-e^U + e^L\right)}{-e^U + e^L - e^{\alpha}(U - L)}$$

We are now in a position to produce the final error formula:

$$\varepsilon(\alpha) = \frac{e^x - c_1 - c_2 x}{e^x} = 1 - \left[\frac{2e^\alpha (1-\alpha)\beta}{\beta - e^\alpha (U-L)} + \frac{2e^\alpha \beta}{\beta - e^\alpha (U-L)}x\right]e^{-x}$$

$$= \left[1 - \frac{2e^\alpha \beta (1-\alpha+x)}{\beta - e^{\alpha (U-L)}}\right]e^{-x} = e^{-x} - \frac{2e^\alpha \beta (1-\alpha+x)e^{-x}}{\beta - e^\alpha (U-L)}, \quad x \in I,$$

where  $\beta = -e^U + e^L$  and  $\alpha$  is given by (6).

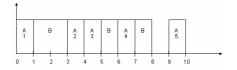

For the 16-interval case, Fig. 7 shows the graphs for the improved approximation and the relative-error function.

Fig. 7. Improved piecewise-linear approximation of the exponential function

The maximum amplitude of the error is

$$\varepsilon_{max} = 6.103433e - 05$$

which translates approximately to 0.3 on our graph. A comparison of this result with (7) finding that the reduction of the maximum error magnitude is 50.00968 percent. And similar remarks to those made at the end of the last section apply equally here.

#### 6 Comparison of Errors

In this section we will compare the average and maximum errors for the discussed two approximation schemas: the one based on condition (C) and the other using the improved condition (IC). Following [7], we define average error as follows. For function  $f: I = [L, U] \rightarrow \mathbf{R}$  approximated by  $\hat{f}: I \rightarrow \mathbf{R}$  the average absolute error is the average value of  $|f(u) - \hat{f}(u)|$  for u uniformly sampled on N points in the interval I. That is,

Average Absolute Error =

$$\frac{\sum_{i=0}^{N-1} \left| f(u_i) - \widehat{f}(u_i) \right|}{N}$$

,

where  $u_i = L + i * \Delta$ , and  $\Delta = \frac{U-L}{N}$ . Similarly, we define the average relative error over the interval I:

Average Relative Error =

$$\frac{\sum_{i=0}^{N-1} \frac{\left|f(u_i) - \hat{f}(u_i)\right|}{f(u_i)}}{N}.$$

Let us also also remind ourselves the definition of the L-infinity norm on the interval I:

Maximum Absolute Error

$$= \max_{u \in I} \left| f(u) - \widehat{f}(u) \right|.$$

Analogously, for the relative error, we will use

Maximum Relative Error

$$= \max_{u \in I} \frac{\left| f(u) - \widehat{f}(u) \right|}{f(u)}.$$

We will use the above definitions to compare the two approximation techniques.

As we have already seen in previous sections the improved schema yields approximately 50 percent maximum error reduction for each of the considered functions. In the sequel we present data showing that error reduction of similar magnitude also happens for the average errors for each of those functions. We also investigate the influence on relative and absolute error of rounding c1, c2to k bits, where k is choosen based on most common applications of a given function. Since for functions  $\sqrt{x}$  and  $\exp(x)$ , k = 16, k = 32 and k = 64 are most important we treat these cases separately. All error values are obtained for the interval I = [0.5, 1] with  $N = 2^{10}$  uniformly sampled points. The precision used in an an actual implementation will, naturally, depend on the particular device employed. For example, given the size of the mutipliers and adders in the Xilinx Virtex-4, 16-bit precision would be ideal.

Table 2 presents results based on condition (C), and Table 3 shows the corresponding values for the improved condition (IC) for  $\sqrt{x}$  and  $\exp(x)$ .

#### 7 Conclusion

The paper shows the use of piecewise-linear interpolation to provide relative error evaluation for certain important elementary functions. Applications to high-performance hardware implementation is also discussed. The square-root function, which is part of the IEEE standard for floating-point arithmetic on all computers is investigated first. Then, the exponential function, which is commonly used in numerical computations, is treated.

In each case we demonstrate that it is possible to find a low-error linear approximation, which can be relatively easily implemented in hardware, resulting in a low-error, high-performance implementation of these mathematical functions.

|                   |             | $c_1,c_2$ | $\sqrt{u}$   | $\exp(u)$    |

|-------------------|-------------|-----------|--------------|--------------|

| absolute<br>error |             | exact     | 3.369593e-05 | 1.740368e-04 |

|                   | average     | 16  bits  | 3.281906e-05 | 1.751525e-04 |

|                   |             | 32 bits   | 3.369593e-05 | 1.740368e-04 |

|                   |             | 64  bits  | 3.369593e-05 | 1.740368e-04 |

|                   |             | exact     | 8.245153e-05 | 3.266860e-04 |

|                   | maximum     | 16  bits  | 7.397733e-05 | 3.369909e-04 |

|                   |             | 32  bits  | 8.245153e-05 | 3.266861e-04 |

|                   |             | 64  bits  | 8.245153e-05 | 3.266860e-04 |

| relative<br>error |             | exact     | 4.066859e-05 | 8.136299e-05 |

|                   | average     | 16  bits  | 3.962489e-05 | 8.172013e-05 |

|                   |             | 32  bits  | 4.066859e-05 | 8.136299e-05 |

|                   |             | 64  bits  | 4.066859e-05 | 8.136299e-05 |

|                   |             | exact     | 1.148435e-04 | 1.220761e-04 |

|                   | $\max$ imum | 16  bits  | 1.030403e-04 | 1.266475e-04 |

|                   |             | 32 bits   | 1.148435e-04 | 1.220762e-04 |

|                   |             | 64  bits  | 1.148435e-04 | 1.220761e-04 |

Table 2. Absolute and relative errors for condition (C)

Table 3. Absolute and relative errors for condition (IC)

|                   |             | $c_1,c_2$ | $\sqrt{u}$    | $\exp(u)$      |

|-------------------|-------------|-----------|---------------|----------------|

| absolute<br>error |             | exact     | 1.541342e-05  | 7.960265e-05   |

|                   | average     | 16  bits  | 1.534050e-05  | 7.934758e-05   |

|                   |             | 32 bits   | 1.541342e-05  | 7.960264e-05   |

|                   |             | 64  bits  | 1.541342e-05  | 7.960265e-05   |

|                   | maximum     | exact     | 4.185535e-05  | 1.659085e-04   |

|                   |             | 16  bits  | 4.298745e-05  | 1.717649e-04   |

|                   |             | 32  bits  | 4.185525e-05  | 1.659085e-04   |

|                   |             | 64  bits  | 4.185535e-05  | 1.659085e-04   |

|                   |             | exact     | 1.860786e-05  | 3.722859e-05   |

|                   | average     | 16  bits  | 1.857589e-05  | 3.706073e-05   |

|                   |             | 32 bits   | 1.860787 e-05 | 3.722858e-05   |

| relative          |             | 64  bits  | 1.860786e-05  | 3.722859e-05   |

| error             |             | exact     | 5.742506e-05  | 6.103433e-05   |

|                   | $\max$ imum | 16  bits  | 5.987699e-05  | 6.531079 e- 05 |

|                   |             | 32  bits  | 5.742520e-05  | 6.103440e-05   |

|                   |             | 64 bits   | 5.742506e-05  | 6.103433e-05   |

### References

- Muller, J.M.: Elementary Functions: Algorithms and Implementation. Birkhauser, Boston, USA, 1997.

- [2] Omondi, A.R.: Computer Arithmetic Systems: Algorithms, Architecture, and Implementations. Prentice-Hall, UK, 1994.

- [3] Mencer, O, Luk, W.: Parameterized high throughput function evaluation for FP-GAs. Journal of VLSI Signal Processing 36 (2004) 17–25.

- [4] Pizer, S.M., Wallace, V.L.: To compute numerically: concepts and strategies. Little, Brown, Boston, USA, 1983.

- [5] Xilinx. 2004. Virtex-4 User Guide.

- [6] Xilinx. 2004. XtremeDSP Design Considerations: User Guide.

- [7] Massayuki Ito, Naofumi Takagi, Shuzo Yajima: Efficient Initial Approximation for Multiplicative Division and Square Root by a Multiplication with Operand Modification. IEEE Trans. Computers 46(4): 495-498 (1997)

- [8] Waterloo Maple Inc.: Maple 8 Programming Guide, 2002.

# Using Branch Prediction Information for Near-Optimal I-Cache Leakage

Sung Woo Chung<sup>1,\*</sup> and Kevin Skadron<sup>2</sup>

<sup>1</sup> Division of Computer and Communication Engineering, Korea University, Seoul 136-713, Korea swchung@korea.ac.kr <sup>2</sup> Department of Computer Science, University of Virginia Charlottesville 22904, USA skadron@cs.virginia.edu

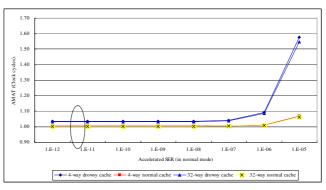

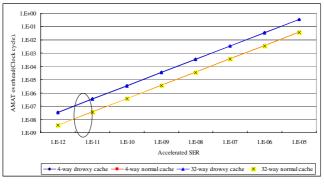

**Abstract.** This paper describes a new on-demand wakeup prediction policy for instruction cache leakage control that achieves better leakage savings than prior policies, and avoids the performance overheads of prior policies. The proposed policy reduces leakage energy by more than 92% with only less than 0.3% performance overhead on average. The key to this new on-demand policy is to use branch prediction information for the wakeup prediction. In the proposed policy, inserting an extra stage for wakeup between branch prediction and fetch, allows the branch predictor to be also used as a wakeup predictor without any additional hardware. Thus, the extra stage hides the wakeup penalty, not affecting branch prediction penalty, in this case, the extra wakeup stage on the normal fetch path can be overlapped with misprediction recovery. With such consistently accurate wakeup prediction, all cache lines except the next expected cache line are in the leakage saving mode, minimizing leakage energy.

Keywords: Instruction Cache, Low Power, Leakage, Drowsy Cache, Branch Prediction.

## **1** Introduction

As process technology scales down, leakage energy accounts for a significant part of total energy. The International Technology Roadmap for Semiconductor [23] predicts that by the 70nm technology, leakage may constitute as much as 50% of total energy dissipation. In particular, the leakage energy for on-chip caches is crucial, since they comprise a large portion of chip area. For instance, 30% of the Alpha 21264 and 60% of the StrongARM are devoted to cache and memory structures [13]. However, cache size can not be decreased to reduce leakage power since cache size is directly related to the performance.

There have been four major circuit techniques to reduce leakage energy dynamically: ABB (Adaptive-reverse Body Biasing) MTCMOS [16], DRG (Data-Retention Gated-ground) [1], Gated-Vdd [17], and DVS for Vdd (which is also called drowsy cache) [3]. In the ABB MTCMOS technique, threshold voltage is dynamically

<sup>\*</sup> Corresponding Author.

C. Jesshope and C. Egan (Eds.): ACSAC 2006, LNCS 4186, pp. 24-37, 2006.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2006

changed but the wakeup penalty between the active mode and the leakage saving mode is long, which makes it difficult for use in L1 caches [4]. DRG retains the data while reducing leakage by gating ground and using remaining leakage to retain cell contents, but the wakeup penalty is long. Thus, this technique may be inappropriate for timing critical caches such as an L1 cache, even if it is effective for less timing critical caches such as L2 [10]. The gated-Vdd technique reduces the leakage power by breaking the connection from the supply voltage (Vdd) or ground (the difference compared to DRG is that a larger sleep transistor is used and cell contents are not preserved) when the cell is put to sleep. While this technique dramatically reduces the leakage, its main disadvantage is that it does not preserve the state of the data in the sleep mode [4]. When the line is needed after it has been put into the leakage saving mode, the line must be refetched from a lower-level memory, which leads not only to additional dynamic energy consumption but also to performance degradation. To prevent these costs, conservative prediction policies should be employed [5][20][21]. Gated-Vdd may, however, be suitable for some L1 data caches where re-fetch penalty is short [12]. Another leakage saving technique is to lower the supply voltage. In this technique, data is not lost when the cache line is in the leakage saving mode (called "drowsy" mode). In the drowsy mode, data is retained, although it can not be accessed for read or write operation. Fortunately, most cache lines are unused for long periods due to temporal locality. Thus, by putting infrequently used cache lines into drowsy mode and keeping frequently accessed cache lines in the active mode, much leakage power is reduced without significant performance degradation. Please note that there is a wakeup penalty to restore the voltage level of the Vdd from the drowsy mode into the active mode. However, the wakeup penalty is expected to be one cycle in 70nm process technology [3]. There has been concern that drowsy cache is more susceptible to soft errors than conventional caches [10]. Fortunately, instructions are read-only and must be protected by parity even in the absence of drowsy techniques. In the infrequent cases when an error is detected, the instruction only has to be refetched.